## FUNDAMENTAL SYSTEMS STRUCTURE

## Core concepts in CPU architecture, the memory hierarchy, compilers, and operating systems

Scott F. H. Kaplan sfkaplan@cs.amherst.edu

## Contents

| 1        | Intr | oduction                                                                                                         | 3  |

|----------|------|------------------------------------------------------------------------------------------------------------------|----|

|          | 1.1  | Why this book?                                                                                                   | 3  |

|          | 1.2  | Topic progression                                                                                                | 4  |

|          | 1.3  | Supporting software                                                                                              | 5  |

|          | 1.4  | How to read this book                                                                                            | 5  |

| <b>2</b> | Dig  | al Logic                                                                                                         | 6  |

|          | 2.1  | A motivating example: Adding two integers                                                                        | 6  |

|          |      | 2.1.1 Binary numbers                                                                                             | 6  |

|          |      | 2.1.2 Addition, take I $\ldots$ | 8  |

|          | 2.2  | Propositional Logic I                                                                                            | 10 |

|          |      | 2.2.1 An example                                                                                                 | 10 |

|          |      | 2.2.2 Generalizing operators                                                                                     | 12 |

|          |      | 2.2.3 Composing propositional functions                                                                          | 12 |

|          |      | 2.2.4 Proper notation $\ldots$  | 13 |

|          | 2.3  |                                                                                                                  | 14 |

|          | 2.4  | Gates and Propositional Logic: Where the rubber meets the road                                                   | 16 |

|          |      | 2.4.1 Water gates                                                                                                | 16 |

|          |      | 2.4.2 Electronic silicon gates                                                                                   | 18 |

|          |      |                                                                                                                  | 18 |

|          | 2.5  |                                                                                                                  | 19 |

|          |      |                                                                                                                  | 19 |

|          |      | 2.5.2 A 4-bit ripple-carry adder                                                                                 | 20 |

|          | 2.6  |                                                                                                                  | 23 |

|          |      |                                                                                                                  | 23 |

|          |      |                                                                                                                  | 24 |

|          |      |                                                                                                                  | 25 |

|          |      |                                                                                                                  | 27 |

|          | 2.7  | 1                                                                                                                | 29 |

|          | -    | 1                                                                                                                | 29 |

## Chapter 1 Introduction

Computing devices are pervasive. A great effort is required, in our society, to avoid their use for all sorts of activities. Some of those activities are obvious: sending email; browsing the web; using a word processor or spreadsheet; playing video games. However, computing devices are used in a much wider variety of devices: cars; airplanes; watches and clocks; mobile telephones; portable music players; televisions; cameras; bank ATM's. However, few people who use these devices understand how they work. That they are so useful to so many people, without those people understanding their structure or inner function, is a testament to their design, hiding their complex inner workings as they perform only seemingly simple tasks.

However, *some people* must understand how these systems are designed and structured. However, for many, the workings of a simple calculator are a mystery, let alone a full-fledged, modern computer system.

## 1.1 Why this book?

Computer systems comprise a large number of *components* or *layers*, and each of these is commonly presented separately from the others. Thus, gaining a fundamental understanding of how such a system could be constructed requires a number of texts and, perhaps, and number of academic courses. Additionally, each of these texts and courses tends to delve into one system component in detail, making it difficult to separate the essential and basic concepts and structures from various refinements and optimizations for that component.

This book, instead, provides a single, unified presentation of the fundamental structure of a complete computing system. It begins with the lowest level—digital logic—and proceeds to compose the capabilities at each level to develop the next. Ultimately, it presents the basic structure of a CPU and memory bus, the design of a compiler, and the structure of an operating system kernel with its basic components. As a whole, this book presents one simple way of developing a complete computing system, bottom to top. It addresses the fundamental concepts required for this design, stripping away the confusing details that come with the development of a full-featured, optimized computing system.

By reading this entire book, or by taking courses that follow the structure of this book, you will ultimately see how a complete computing system works. You will not know the details

of any one real-world system, but you will understand the core concepts that will allow you to grasp those details of any such system. Moreover, you will be able to delve into each component or layer and understand not only the deeper concepts, but also how that layer interacts with others. It is this interaction between layers that is critical to system design and use, but is often lost in the one-component-at-a-time approach taken by most texts and courses.

## **1.2** Topic progression

This text takes a *bottom-up* approach. That is, it will begin with the most simple tools and concepts, and then build them up, one layer at a time, toward more complex and capable tools and concepts. Specifically, we should end with a complete (if simplified) computing system for which we can write complex programs and run many of them at once.

This approach is in contrast to the (predictably named) *top-down* approach. For that approach, the text would have begun with a complete, programmable computing system, and then explained its workings by incrementally delving down to the more simple and detailed layers. Each of these two approach has advantages and disadvantages. Examination of them will reveal why this book takes the bottom-up approach.

The top-down approach has the advantage that the motivation for each layer, as the presentation progresses, is clear. If you begin with the premise that you want a computer system for which you can write and run multiple, complex programs, then it is clear **why** one would begin the presentation with such a system. In order to understand how that system works, you then begin to delve down into the layers below it, carrying with you the clear motivation for understanding those layers.

The bottom-up approach lacks this ease of motivation. For example, when beginning with something so simple as *digital logic*, it is not immediately and intuitively clear to the reader **why** this topic is relevant. It is therefore the responsibility of the writer to explicitly provide the motivation for understanding this layer of the system, while deferring any understanding of how this topic relates to the entire system.

In spite of this problem with the bottom-up approach, is does have one wickedly important advantage: there need not be any mysteries. When beginning with the most simple layer, everything about that layer—its concepts, implementation, and applications—can all be explicitly explained. Then, with the advantage of fully understanding that lowest layer, the presentation can progress to the next layer, drawing upon the fully demystified layer below. In this way, when the presentation may reach its top level—a complete computational system—then every aspect of the system is explained and understood. No component is a mystery, and the interaction and function of all components can be seen.

In contrast, the top-down approach suffers from seemingly mysterious components, layers, and concepts until the very end is reached. When you begin with the complete system, none of its workings are understood. As you delve into the lower layers, you learn how each layer works, but you do so by making assumptions about the yet uninvestigated layers below, whose workings are a mystery. As you uncover the mystery of each layer, you must remember how it relates to the layers above it, and, *ex post facto*, piece together their relationship.

The purpose of this text and courses that follow it is to **demystify** the workings of com-

putational systems. Therefore, it is more important that, during the journey of discovery, nothing is left as a mystery. At every step, you should see how the current topic is supported by all of the levels below it, with full knowledge of the concepts and the implementation of those levels. We therefore will follow the bottom-up approach, explicitly motivating each level, and building upon tools and concepts that have already been thoroughly developed.

## 1.3 Supporting software

[SFHK: ADD THIS WHEN THE SIMULATOR/ASSEMBLER/COMPILER ARE DONE.]

## 1.4 How to read this book

[SFHK: WRITE ME]

# Chapter 2 Digital Logic

You have likely heard that computers work in "binary"—all 0's and 1's. But what does that **mean?** How can a collection of 0's and 1's represent numbers, or text, or pictures, or movies? How cna a program be made of nothing but 0's and 1's? That is, how can a group of 0's and 1's tell a machine **what to do** and **when to do** it?

We will answer some of these questions directly. For example, representing everyday numbers, such as 3,127, is merely a matter of learning base-2 numeric representation, which is addressed in Section 2.1.1. However, more complex computing activities, such as using YouTube, are much more difficyult to grasp at the level of 0's and 1's. Doing so is akin to trying to understand a recipie for pumpkin pie by examining the interactions of the electrons, protons, and neutrons in a cookbook.

Although all modern computing is ultimately the manipulation of these 0's and 1's, computers cannot really be understood only at that level. Computer systems are better understood as a collection of *layers*, where the manipulation of binary numbers are at the bottom layer, and complex activities like Google Earth are at or near the top.

This chapter addresses that lowest level upon which all computing systems are built. It will build the foundation for representing and manipulating the 0's and 1's. Directly upon that foundation, we will be able to build circuits that perform basic arithmetic functions; later, we will use other, similar circuits that act as *memory* to store 0 and 1 values—data—for later.

## 2.1 A motivating example: Adding two integers

Of all the complex calculations and operations that a computing device can perform, among the most simple and intuitively understandable is *integer addition*. specifically, let us consider the addition of two *whole numbers*—non-negative integers (0, 1, 2, ...). How can we make a machine that will add any two such numbers (e.g., 45, 127 + 6, 056)?

#### 2.1.1 Binary numbers

Knowing that we will later use devices that can manipulate 0's and 1's, we will begin by translating our problem into that form. That is, we want to represent the two values to be

| decimal | binary |

|---------|--------|

| 0       | 0      |

| 1       | 1      |

| 2       | 10     |

| 3       | 11     |

| 4       | 100    |

| 5       | 101    |

| 6       | 110    |

| 7       | 111    |

| 8       | 1000   |

| 9       | 1001   |

| 10      | 1010   |

| 11      | 1011   |

| 12      | 1100   |

| 13      | 1101   |

| 14      | 1110   |

| 15      | 1111   |

| 16      | 10000  |

| 17      | 10001  |

| 18      | 10010  |

| 19      | 10011  |

| 20      | 10100  |

Table 2.1: The integers 0 to 20 in both decimal and binary.

added (the *inputs*) as well as their resulting sum (the *outputs*), using only the digits 0 and 1.

Typically, people represent numbers using the set of digits from 0 to 9, also known as *base* 10 or *decimal notation*. Here, we need to represent numbers in *base* 2 or *binary notation*. We will use the *binary digits*—*bits*, for short—0 and 1.

When counting in decimal, we can imagine an odometer. When the 1's position contains the final digit, 9, and we then want to advance to the next number, the 1's position "rolls over" to a 0 again while the adjacent 10's position advances to a 1. More generally, each position advances from 0 to 9, and then it will return to 0 as the next, more significant position advances by one digit.

For binary numbers, imagine an odometer for which each position cycles not though the digits from 0 to 9, but only through the digits from 0 to 1. If the digit at a position is a 1, and we want to advance the counter to the next number, then that position "wraps around" to 0 and advances the digit at the next, more significant position. For example, Table 2.1 shows the whole numbers from 0 to 20.

To further develop an intuition about binary notation, consider how to decompose the digits of a decimal number into digits of differing significance. For example, 6,398 can be decomposed into 6 thousands, 3 hundreds, 9 tens, and 8 ones. We can represent this decomposition as a collection of multiplications and additions, as shown in Table 2.2. Of course, the sum of the decomposed values shown in the bottom row is the original number.

| thousands | hundreds | tens     | ones     |

|-----------|----------|----------|----------|

| 6         | 3        | 9        | 8        |

| ×         | ×        | ×        | ×        |

| $10^{3}$  | $10^{2}$ | $10^{1}$ | $10^{0}$ |

| П         | П        | П        | П        |

| 6,000     | 300      | 90       | 8        |

Table 2.2: Decomposition of the decimal number 6, 398.

| thirty-seconds | sixteens | eights  | fours   | twos    | ones     |

|----------------|----------|---------|---------|---------|----------|

| 1              | 0        | 1       | 1       | 0       | $1_{2}$  |

| ×              | ×        | ×       | ×       | ×       | ×        |

| $2^{5}$        | $2^{4}$  | $2^{3}$ | $2^{2}$ | $2^{1}$ | $2^{0}$  |

| П              | П        | П       | П       | П       | П        |

| 32             | 0        | 8       | 4       | 0       | $1_{10}$ |

Table 2.3: Decomposition of the number  $101101_2 = 45_{10}$ .

Binary numbers are similar, but instead of there being positions for 1's, 10's, 100's, etc., there are positions for 1's, 2's, 4's, 8's, etc. Table 2.3 shows an example of decomposing a binary number. In this table, notice that, now that we are using two numerical notations, each value is tagged with a subscript of 2 or 10 to indicate whether the value is binary or decimal, respectively. Also notice that if you sum the decimal values into which the binary number is decomposed, you obtain the decimal reprensentation of the same number—that is, you will have converted the binary representation into a decimal one.

Much like each decimal number can be decomposed into a sum of power-of-10 units, binary numbers are decomposed into a sum of power-of-2 values. More importantly, **any** whole number can be represented in either decimal and binary—the two are equivalent. We should also note the difference between a *number* and its *representation*. No matter the representation of a number—45 (decimal), 101101 (binary), XLV (roman numerals)—the underlying number that these symbols represent is the same.

### 2.1.2 Addition, take I

In order to determine what concepts and devices we need to perform addition, we must first see how binary addition is performed. Let us review the simple mechanics of decimal addition. The two values to be added must be aligned by positions of significance: the 1's must be aligned, as must the 10's, 100's, etc. As an example, consider the additon of two four-digit decimal numbers:  $x = 3,281_{10}$  and  $y = 4,753_{10}$ . We decompose the variables that represent these values to ease presentation of the arithmetic steps. Specifically,  $x = (x_3, x_2, x_1, x_0)$ , where  $x_3 = 3$ ,  $x_2 = 2$ ,  $x_1 = 8$ , and  $x_0 = 1$ . Similarly,  $y = (y_3, y_2, y_1, y_0)$ , and for this specific example,  $y_3 = 4$ ,  $y_2 = 7$ ,  $y_1 = 5$ , and  $y_0 = 3$ . Thus, our addition operation begins with the configuration shown in Table 2.4. On the left, we see the configuration for the addition of the specific values from our example; on the right, we see the generalized operation only on variables.

|   | 3 | 2 | 8 | 1 |   | $x_3$ | $x_2$ | $x_1$ | $x_0$ |

|---|---|---|---|---|---|-------|-------|-------|-------|

| + | 4 | 7 | 5 | 3 | + | $y_3$ | $y_2$ | $y_1$ | $y_0$ |

Table 2.4: Configuration of addition for both example values (on the left) and generalized variables (on the right).

|   | 1 | 1 | 0 | $0_{10}$                     |       | $c_3$ | $c_2$ | $c_1$ | $c_0$ |

|---|---|---|---|------------------------------|-------|-------|-------|-------|-------|

|   | 3 | 2 | 8 | $1_{10}$                     |       | $x_3$ | $x_2$ | $x_1$ | $x_0$ |

| + | 4 | 7 | 5 | $0_{10} \\ 1_{10} \\ 3_{10}$ | +     | $y_3$ | $y_2$ | $y_1$ | $y_0$ |

| 0 | 8 | 0 | 3 | $4_{10}$                     | $c_4$ | $r_3$ | $r_2$ | $c_1$ | $c_0$ |

Table 2.5: The result of carrying out the addition algorithm on a specific set of values (on the left) and generalized variables (on the right).

Having formatted the input values as needed, summing x and y follows this algorithm:

- 1. Let k be the number of digits in the inputs (or, if they are not of the same length, prepend 0 digits to the shorter one to make it them the same length).

- 2. Let i = 0, where i indicates the position whose values to add.

- 3. Let  $c_0 = 0$ , which is the carry-in to the least significant column. Write that value above  $x_0$ .

- 4. Let  $z_i = x_i + y_i + c_i$ . This result,  $z_i$ , is a two-digit result that we decompose as  $z_i = c_{i+1}r_i$ .

- 5. Write  $r_i$  below  $x_i$  and  $y_i$ . Write  $c_{i+1}$  above  $x_{i+1}$  and  $y_{i+1}$ .

- 6. Increment i.

- 7. If i < k then jump back to step 4.

- 8. Move  $c_k$  to the left of  $r_{k-1}$ , completing the result.

When we apply this algorithm, the result appears as shown in Table 2.5.

This same algorithm can be used for adding binary numbers as well. The only difference is in how  $r_i$  and  $c_i$  are determined—that is, how **three** binary digits  $(x_i, y_i, \text{ and } c_i)$  are added.

For example, consider adding  $x = 1011_2$  and  $y = 0110_2$ . In order to see how this addition progresses, we must consider the possible values that may occur in step 4. One advantage of binary is, given only two possible digits, one can often exhaustively list all of the possible inputs and outputs, known as a *truth table*. Here, we consider adding three one-bit values  $c_i$ ,  $x_i$ , and  $y_i$ ). Since each can only take the value 0 or 1, we can construct Table 2.6. Each of the eight possible sums is shown, in decimal, as z, and then as the two-bit binary value  $c_{i+1}r_i$ .

We can then lay out the numbers or variable using the same configuration that we do for decimal values, and then carry out the addition, using the values in Table 2.6 to determine the results in step 4. We see how the binary addition is performed in Table 2.7.

| $c_i$ | $x_i$ | $y_i$ | z | $c_{i+1}$ | $r_i$ |

|-------|-------|-------|---|-----------|-------|

| 0     | 0     | 0     | 0 | 0         | 0     |

| 0     | 0     | 1     | 1 | 0         | 1     |

| 0     | 1     | 0     | 1 | 0         | 1     |

| 0     | 1     | 1     | 2 | 1         | 0     |

| 1     | 0     | 0     | 1 | 0         | 1     |

| 1     | 0     | 1     | 2 | 1         | 0     |

| 1     | 1     | 0     | 2 | 1         | 0     |

| 1     | 1     | 1     | 3 | 1         | 1     |

Table 2.6: The truth table for adding three one-bit values.

|   |   |   |   | $0_{2}$ |       |       | $c_2$ |       |       |

|---|---|---|---|---------|-------|-------|-------|-------|-------|

|   | 1 | 0 | 1 | $1_{2}$ |       | $x_3$ | $x_2$ | $x_1$ | $x_0$ |

| + | 0 | 1 | 1 | $0_2$   | +     | $y_3$ | $y_2$ | $y_1$ | $y_0$ |

| 1 | 0 | 0 | 0 | $1_{2}$ | $c_4$ | $r_3$ | $r_2$ | $c_1$ | $c_0$ |

Table 2.7: The result of carrying out the addition algorithm on a specific set of values (on the left) and generalized variables (on the right).

## 2.2 Propositional Logic I

We now know how to carry out a stepwise process—an *algorithm*—to add two binary numbers. However, we must develop a number of concepts in order to design a machine capable of automatically performing addition.

At the base of these concepts—indeed, at the bottom of all computational devices—is *propositional logic*. Specifically, it is the set of formal rules for handling everyday concepts like *and*, *or*, and *not*.

#### 2.2.1 An example

As an example, consider the following statement:

Tomorrow, if it is not raining, and if the temperature is at least 80°F, then we will go to the beach.

This statement defines two conditions that must be evaluated to determine whether a visit to the beach will occur. These two conditions are:

1. A = not raining

2.  $B = temperature \ge 80^{\circ} F$

We can further decompose condition 1 as:

• A' = raining

| X | $\bar{X}$ |

|---|-----------|

| F | Т         |

| Т | F         |

| 1 | г         |

Table 2.8: The truth table that defines the NOT operator.

| X | Y            | X and $Y$    |

|---|--------------|--------------|

| F | $\mathbf{F}$ | F            |

| F | Т            | $\mathbf{F}$ |

| Т | $\mathbf{F}$ | $\mathbf{F}$ |

| Т | Т            | Т            |

Table 2.9: The truth table that defines the AND operator.

•  $A = \operatorname{NOT}(A')$

So, we can express whether the conditions for a beach trip are met as:

$$C = A \text{ and } B$$

A, B, and C are Boolean variables: they can take on one the values of true (T) or false (F). In this example, we must ultimately determine the value of C. To do that, we need to know both whether it is raining, and the temperature.

First, whether it is raining is itself a Boolean condition—either it is raining or it is not. Thus, we can assign the value T to A' if it is raining, and F to A' if it is not.

Having assigned one of those values to A', we can determine the value of A. To do so, we must define the logic operator NOT. It is a *unary* operator, which means that it takes a single Boolean variable as its input. We can define the relationship between the two possible input values that the single variable may be assigned and the possible output values of the operator with the truth table shown in Table 2.8. This table shows that the NOT operator simply inverts the input value: F becomes T; T becomes F.

Second, the temperature is **not** a Boolean value; it is, instead, a real-numbered value. However, we rely on the comparison operator greater than or equal to  $(\geq)$ , which takes two real-valued inputs and produces a Boolean output value. Thus, *B* can be assigned the result of comparing the temperature to 80°F: either the temperature is at least 80°F (*B* = T), or it is not (*B* = F).

Third, given the ability to determine the Boolean values of A and B, we must determine how the logic operator AND functions to calculate C. Again, a truth table can be used to formally define the commonsense notion that C = T if and only if A = B = T. Table 2.9 shows this truth table.

Ultimately, to evaluate C, one must apply the comparison operator to determine B. Moreover, the NOT operator should then be applied to determine A. Finally, the AND operator must be applied to A and B in order to obtain the final result.

| X | Y            | X or $Y$ | X XOR $Y$    | X nor $Y$    |

|---|--------------|----------|--------------|--------------|

| F | $\mathbf{F}$ | F        | F            | Т            |

| F | Т            | Т        | Т            | $\mathbf{F}$ |

| Т | $\mathbf{F}$ | Т        | Т            | $\mathbf{F}$ |

| Т | Т            | Т        | $\mathbf{F}$ | $\mathbf{F}$ |

Table 2.10: The truth table that defines the *inclusive or* (OR), *exclusive or* (XOR), and *neither nor* (NOR) operators.

| $X_3$ | $X_2$        | $X_1$        | $X_0$ | R |

|-------|--------------|--------------|-------|---|

| F     | F            | F            | F     | Т |

| F     | $\mathbf{F}$ | $\mathbf{F}$ | Т     | Т |

| F     | $\mathbf{F}$ | Т            | F     | F |

| F     | $\mathbf{F}$ | Т            | Т     | F |

| F     | Т            | $\mathbf{F}$ | F     | F |

| F     | Т            | $\mathbf{F}$ | Т     | Т |

| F     | Т            | Т            | F     | F |

| F     | Т            | Т            | Т     | F |

| Т     | $\mathbf{F}$ | $\mathbf{F}$ | F     | Т |

| Т     | $\mathbf{F}$ | $\mathbf{F}$ | Т     | Т |

| Т     | $\mathbf{F}$ | Т            | F     | Т |

| Т     | $\mathbf{F}$ | Т            | Т     | F |

| Т     | Т            | $\mathbf{F}$ | F     | Т |

| Т     | Т            | $\mathbf{F}$ | Т     | Т |

| Т     | Т            | Т            | F     | F |

| Т     | Т            | Т            | Т     | F |

Table 2.11: The truth table for an arbitrary, 4-input, Boolean logic operator.

### 2.2.2 Generalizing operators

Moving away from this simple example, we can generalize this type of calculation on Boolean values by defining other binary (that is, *two-input*) operators (of which AND is one). Consider Table 2.10, which is a truth table for the *inclusive or* (OR), *exclusive or* (XOR), and *neither nor* (NOR) operators. Notice that although each of these binary operators can be given a name that is a commonsense English word, that need not be the case. A logic operator can accept **any** number of Boolean value inputs, and its output values may follow no commonsense pattern. Consider the quanternary logic operator in Table 2.11, for which no simple name could be given. This example shows that any combination of input of output values listed in a truth table can define a valid operator.

## 2.2.3 Composing propositional functions

As we saw in the example in Section 2.2.1, propositional statements can be composed by applying additional propositional logic operators to any existing propositional expression. These compositions create new logic operations that can be expressed as truth tables of

| A | B   | A and $B$ | C = A nand $B$ |

|---|-----|-----------|----------------|

| F | ' F | F         | Т              |

| F | Т   | F         | Т              |

| Г | ' F | F         | Т              |

| Г | Т   | Т         | F              |

Table 2.12: Composing AND and NOT yields the NAND operator.

their own. For example, consider composing the AND and NOT operators:

$$C = \text{NOT} (A \text{ AND } B)$$

We can evaluate C for all possible input values of A and B, yielding the truth table shown in Table 2.12.

We can also decompose known operators into compositions of other (usually "simpler") operators. Consider two of the binary operators from Table 2.10: NOR and XOR can both be expressed in terms of AND, OR, and NOT:

$$C = \text{not} (A \text{ or } B) = A \text{ nor } B$$

$$C = (A \text{ or } B) \text{ and } (\text{not } (A \text{ and } B)) = A \text{ xor } B$$

We will later see, in Section 2.6.3, that AND, OR, and NOT are sufficient to compose **any** logic function. For now, it is sufficient to note that any combination of input and output values define such a logic function that can be expressed using some composition of operators.

#### 2.2.4 Proper notation

So far, we have written out the use of Boolean operators in a kind of longhand, writing AND, NOT, etc. explicitly in our expressions. However, we will heretofore use a more compact notation—one that resembles typical algebraic notation. Specifically:

• Negation: A bar over any variable or expression is the negation of that expression. That is:

$$C = \operatorname{NOT}(A) \Rightarrow C = \overline{A}$$

• **Conjunction:** Rather than writing the operator AND to conjoin two expressions, they need only to be written next to one another, much like algebraic multiplication:

$$C = A$$

and  $B \Rightarrow C = AB$

• **Inclusive disjunction:** The inclusive OR operator is written using the plus sign, much like algebraic addition:

$$C = A \text{ or } B \Rightarrow C = A + B$$

Table 2.13: The four possible summations of two 1-bit values.

$$\begin{array}{c} x \\ + y \\ \hline z_1 & z_0 \end{array}$$

Table 2.14: Generalizing the addition of two 1-bit values, using variables for each participating bit value.

• Exclusive disjunction: The exclusive XOR operator has no "normal" algebraic analog, and is written as a modified form of addition:

$$C = A \operatorname{xor} B \Rightarrow C = A \oplus B$$

This notation can be composed just as the operators themselves are, thus sufficing to express other operators:

- NAND: C = A NAND  $B \Rightarrow C = \overline{AB}$

- NOR: C = A NOR  $B \Rightarrow C = \overline{A + B}$

## 2.3 Binary addition meets propositional logic

Now we can make good on putting propositional logic to use. More specifically, we can recast the arithmetic addition of binary numbers as logic expressions. For simplicity, let us begin with the addition of two 1-bit integers. There are only four possible combinations of two 1-bit values for addition, shown in Table 2.13.

We can generalize these additions by naming the 1-bit inputs x and y, and the 2-bit output value z. The relationships between these variable is shown in Table 2.14.

Let us recast the addition of x and y as a problem of propositional logic. Consider a binary value of 0 as thought it were a Boolean value F; likewise, the binary value 1 can be substituted for the Boolean T. thus, we can map the above listing of 1-bit addition values onto the truth table shown in Table 2.15. Examining the two output columns for z in this table, we see that each can be expressed as simple logic expressions:

$$z_1 = xy$$

$$z_0 = x \oplus y$$

Thus, this simple arithmetic calculation can be recase as a pair of propositional logic functions. For any pair of 1-bit numbers, the application of the AND and XOR logic operators will produce the arithmetic sum.

| x | y | $z_1$        | $z_0$        |

|---|---|--------------|--------------|

| F | F | F            | F            |

| F | Т | F            | Т            |

| Т | F | $\mathbf{F}$ | Т            |

| Т | Т | Т            | $\mathbf{F}$ |

Table 2.15: The summation of two 1-bit values (x and y), producing a 2-bit result (z), cast as a truth table.

Addition of 1-bit numbers is so simple that its illustrative capacity as an example is limited. Let us consider the addition of 4-bit integers, which will provide a model for the addition of any two *n*-bit integers for any choice of n > 1. With two 4-bit values, it is impractical to enumerate all of the possible input combinations. However, we can use the model from Section 2.1.2, where the input values x and y are symbolically decomposed into their bits:  $x = (x_3, x_2, x_1, x_0); y = (y_3, y_2, y_1, y_0)$ . Moreover, the addition produces both a set of result bits  $r = (r_3, r_2, r_1, r_0)$  and a set of "carry" bits  $c = (c_4, c_3, c_2, c_1)$ . Specifically, recall the form, following standard pencil-and-paper addition of decimal integers shown in Table 2.4.

To cast this arithmetic problem instead as a series of propositional logic expressions, we must find a logical relationship between each of the bits of r and c in terms of the bits of x and y. Note that we can begin with the least significant input bits— $x_0$  and  $y_0$ —since adding those is merely adding two 1-bit values, which we have already examined. Therefore:

$$r_0 = x_0 \oplus y_0$$

$$c_1 = x_0 y_0$$

The remaining, more significant positions are slightly more complex. However, Table 2.6, which relates the input bits  $c_i$ ,  $x_i$ , and  $y_i$  to the output bits  $r_i$  and  $c_{i+1}$  for position i, is exactly the correct truth table for this task, where this truth table substitutes the binary value 0 for the Boolean value F, and the binary value 1 for the Boolean value T. From that table, we can derive the following formulae for the output bits of each column.<sup>1</sup>

$$r_i = \bar{c}_i \bar{x}_i y_i + \bar{c}_i x_i \bar{y}_i + c_i \bar{x}_i \bar{y}_i + c_i x_i y_i$$

$$c_{i+1} = \bar{c}_i x_i y_i + c_i \bar{x}_i y_i + c_i x_i \bar{y}_i + c_i x_i y_i$$

Thus, the addition of our input bits can produce the carry and result bits by applying these logic functions. One needs only to carry out the evaluation of the propositional logic operators; yet the larger result is an arithmetic one.

<sup>&</sup>lt;sup>1</sup>If the source of these formulae is a mystery, see Section 2.6.3, which presents a standardized approach for converting truth tables to logic functions.

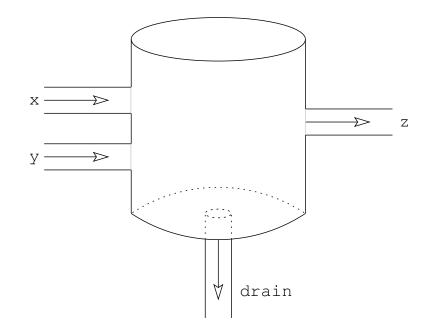

Figure 2.1: Schematic of an AND gate constructed from a drum and connected pipes through which water flows (or not).

## 2.4 Gates and Propositional Logic: Where the rubber meets the road

So far, we have seen how to decompose at least one simple arithmetic calculation into a collection of propositional logic operations. What has been unclear is **why** we are interested in this decomposition. We answer that question here: *gates*.

Our interest in propositional logic stems from our ability to make physical devices that carry out logic operations. These devices serve as the fundamental building blocks for all computation, because **all** computational expression can ultimately be decomposed into logic functions. Our goal here is to establish how these devices can be used to carry out **any** logic operation.

#### 2.4.1 Water gates

**AND gate:** For a first attempt at creating devices that can carry out logic operations, we will employs devices that control the flow of water. how the water flows determines the result of some logic operation. As an example, let us begin with a water-flow device that carries out the AND operation, specifically: z = xy.

Figure 2.1 shows a drum to which there are four pipes of equal gauge attached. Each input and output is associated with one pipe each. For the inputs x and y, we can represent a value of 1 (or T) by pumping water in through their respective pipes. Likewise, we can represent 0 (or F) by **not** pumping any water in through either or both of these pipes. We also interpret a flow out through the z pipe as a 1, and no flow as a 0. The flow of water (or lack of it) trhough the drain pipe is not relevant, so we ignore it.

How does this drum carry out the logical AND operation? How does it behave as an "AND gate"? Let us consider all four possible input combinations:

- Case  $00_2 x = 0$  and y = 0: No flow enters the drum through the x and y pipes. Therefore, no flow exists the z pipe, implying that z = 0, which is the correct result for AND.

- Case  $01_2 x = 0$  and y = 1: No flow enters through the x pipe, but it **does** enter through the y pipe. The water that flows in through y then flows out of the drum through the *drain* pipe. Since the drain allows the water to exit the drum as fast as it enters, the water level never rises to the z pipe, and thus no water flows out through the z pipe. Thus, the device emits z = 0, which is correct.

- Case  $10_2 x = 1$  and y = 0: This case is analogous to the previous case  $01_2$ .

- Case  $11_2 x = 1$  and y = 1: Flow enters the drum through both the x and y pipes. Because the water exits the *drain* pipe at half the rate of the total incoming flow, the water level will rise in the drum. After some time—a period knows as the *gate delay*—water will begin flowing out of the z pipe. This outflow represents the correct result for this case of z = 1.

Because of the gate delay for case  $11_2$ , one must wait for at least that period of time after presenting new input flows (or lack of them) before the output of z is guaranteed to be correct. In any previous moment, the gate may still be altering the water level, and the output may not yet be stable. For different gate designs, the gate delay may have slightly different causes, and the duration of the delay will vary.

**OR gate:** Let us now consider how to construct an OR gate from this type of water drum. Constructing such a gate requires only that we swap the labels of the *drain* and *z* pipes from the water-drum AND gate. To see that this simple inversion works, consider the four possible input cases:

- Case  $00_2 x = 0$  and y = 0: Input flow from neither the x nor y pipes implies no output flow through the z pipe, implying correctly that z = 0.

- Cases  $01_2$  and  $10_2$ —x = 0 and y = 1; or x = 1 and y = 0: The flow into the drum from one of the two inputs flows out of the z input, yielding the correct result of z = 1.

- Case  $11_2 x = 1$  and y = 1: The flow into the drum from both x and y pipes will cause both a flow out of the z pipe **and** a raising of the water level in the drum. That excess water will eventually flow harmlessly out of the *drain* pipe. The flow out of the z pipe implies the correct result of z = 1.

Notice that for this OR gate, the gate delay is much shorter. When new input flow is presented, one must wait only the time required for the water to fall down the drum and begin exiting the z pipe. Thus, thr output of this OR gate is guaranteed to be correct more quickly than the AND gate.

**NOT gate:** We are missing one critical capability—a gate that performs logical negation. We need a device that carries out  $z = \bar{x}$ . Notice that, unlike the other two gates that we have devised, this one must produce an output flow when there is **no** input flow. therefore, it must have a "power source"—an input flow that is not one the logical arguments to the operator. We leave it as an exercise to you, the reader, to device a water-drum NOT gate that...

- ... when x = 0, the flow from the power source is directed to flow out of the z pipe, and ...

- ... when x = 1, the flow from both x and the power source is directed to flow out of *drain* pipes.

### 2.4.2 Electronic silicon gates

The water-drum gates presented in Section 2.4.1 are meant to show the simple construction of devices capable of performing propositional logic operations. Of course, these water drums would operate correctly, but slowly. Real computing devices use semiconducting<sup>2</sup> silicon transistors instead of drums, and flowing electricity instead of flowing water. Typically, a flow of +5 volts represents a binary value of 1, while 0 volts represents a value of 0. Other than these changes in substrate, the functions of the silicon gates and the water gates are quite similar, but the former are **much** faster.

The construction of the silicon gates is beyond the scope of this book. [SFHK: ADD REFERENCES TO DESCRIPTIONS OF TRANSISTORS, SILICON GATES, AND LITHOGRAPHY.]

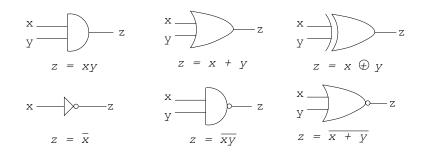

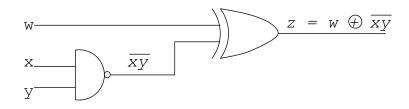

### 2.4.3 Representing logic functions with gates

No matter the specific devices used, we will heretofore represent these logic gates as depicted in Figure 2.2. Critically, these gates can be composed analogously to the manner in which logic operators are algebraically composed. For example, Figure 2.3 shows an example of the composed logic function  $z = w \oplus \overline{xy}$ . The order in which a Boolean algebraic expression is evaluated is mirrored by the order in which input values flow into and through the gates, and ultimately to the circuit's output. In this example, one must first evaluate  $\overline{xy}$ ; only then can the result of that evaluation be combined with w using the XOR operator to produce the result z. Analogously, the inputs lines x and y must have their values flow through the NAND gate first, then having the output of that gate flow as an input, along with the w line, into the XOR gate.

In closing this section, let us remember the high-level impact of composing gates in this manner: we can contruct a device that automatically computes the result of any propositional logic function for a set of given input values. Thus, any problem that can be expressed as a logic function can also be computed automatically by some arrangement of gates.

<sup>&</sup>lt;sup>2</sup>That is, electrically conductive under some circumstances, but non-conductive under others.

Figure 2.2: Substrate-neutral, graphical representations of gates that implement various logic operations.

Figure 2.3: A gate-based circuit that implements the function  $z = w \oplus \overline{xy}$ .

## 2.5 Foreshadowing: Basic adder circuits

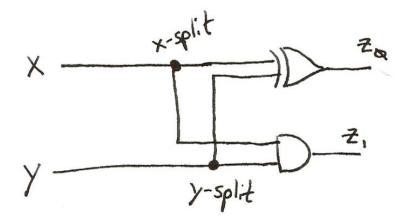

In Section 2.3, we saw how to express arithmetic addition of both 1-bit and 4-bit whole numbers as collections of logic functions. Here, we show hot o translate those logic functions into gate-based circuits, thus designing devices capable of carrying out these addition operations automatically.

#### 2.5.1 A 1-bit half-adder

Recall that, in adding two 1-bit values—x and y—that two propositional logic functions are required to produce each of the values from the 2-bit result. Specifically, the result  $z = (z_1, z_0)$  is determined by the functions:

$$z_0 = x \oplus y$$

$$z_1 = xy$$

Figure 2.4 a circuit to carry out this addition task, we can use the **same** two inputs to feed into gates that implement both logic functions and produce both output bits. Notice that any line that carries a flow can be split so that it can serve as an input to more than one gate. For example, x is divided at the dot labeled *x-split*, and then procides the same input value to both gates simultaneously. This dot is used to show the coinnection all line that meet at that point. Lines that cross without such a dot are not connected.

This combinational circuit implements 1-bit arithmetic addition. Present any two values as x and y, pause for the gate delay of both gates, and observe  $z_1$  and  $z_0$  to obtain the answer.

Figure 2.4: A half-adder that adds two 1-bit values.

#### 2.5.2 A 4-bit ripple-carry adder

Adding 1-bit numbers provides a useful initial example, but it does not demonstrate well the more complex structures that can be devised to compute more complex problems. To provide a richer example, we examine the logic and circuitry for a 4-bit adder.

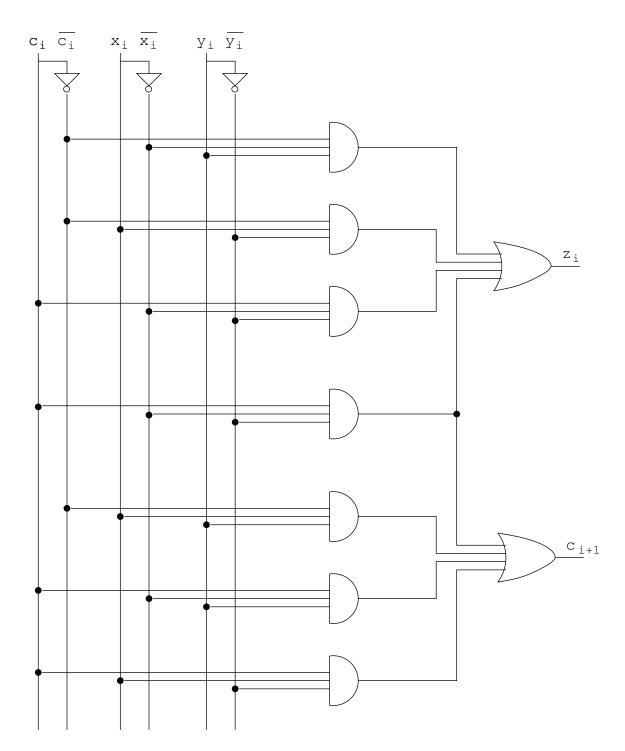

Recall that the addition of 4-bit values can be represented in the form shown in Figure 2.7. In that formulation,  $x = (x_3, x_2, x_1, x_0)$  and  $y = (y_3, y_2, y_1, y_0)$  are input values, while  $z = (z_3, z_2, z_1, z_0)$  and  $c = (c_4, c_3, c_2, c_1)$  are 4-bit output values produced by the process of adding x and y. More specifically, recall that adding one set of bits of the same significance is defined by the formulas:

$$z_i = \bar{c}_i \bar{x}_i y_i + \bar{c}_i x_i \bar{y}_i + c_i \bar{x}_i \bar{y}_i + c_i x_i y_i$$

$$c_{i+1} = \bar{c}_i x_i y_i + c_i \bar{x}_i y_i + c_i x_i \bar{y}_i + c_i x_i y_i$$

Figure 2.5 shows these two logic functions as combinational circuits. Collectively, we call these circuits a *full-adder*, since, unlike the half-adder, it incorporates the carry-in value. Furthermore, it produces the output for a single column's result  $(z_i)$  as well as the input for the next column  $(c_{i+1})$ . Now that we know how this full-adder is structured, we can draw it as a box with its three 1-bit inputs and its two 1-bit outputs, with no need to draw each individual gate.

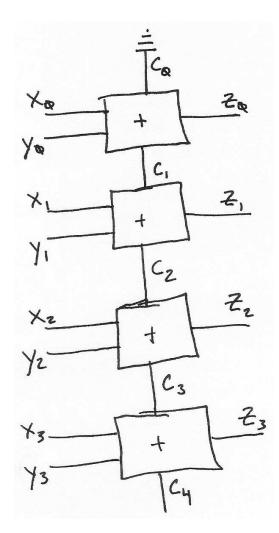

Clearly, a full-adder is not, by itself, capable of adding two 4-bit values. However, by stringing together a sequence of four full-adders, we can construct a 4-bit adder. The key observation is that the carry-out of one full-adder may be connected to the carry-in of the next, thus properly carrying those value from a less significant column to the next more significant one.

Figure 2.5: A full-adder that adds three 1-bit values.

Figure 2.6 shows how four full-adders can be arranged to add two 4-bit values. First, notice that  $c_0$  seems to be a superfluous input. By setting  $c_0 = 0$ , we ensure that this extraneous input has no effect on the result. In the diagram, the triangle-like sequence of lines that serve as a source for  $c_0$  is the symbol for connecting a line directly to ground—that is, this line will carry 0 volts to represent the input value of 0.

Figure 2.6: A 4-bit ripple-carry adder constructed from a chain of full-adders.

Second, notice that  $c_1$ ,  $c_2$ , and  $c_3$  are both input **and** output values. This dual role reflects directly the role of carry digits in pencil-and-paper addition—the "excess" of one column in *carried* into the next.

Third, recall the issue of gate delay (define in Section 2.4.1). If we present all of the inputs at time  $t_0$ , then we cannot trust the outputs of the least significant full-adder ( $z_0$  and  $c_1$ ) until the accumulated gate delay has passed. If we peek inside out full-adder circuit, we see each of the outputs is the result of waiting for a group of NOT gates, then a group of AND gates, and finally a multi-input OR gate (which may be implements as a collection of 2-input OR gates). Critically, all of the NOT gates do their work at the same time—*concurrently*. The same is true of the AND gates, and of the two OR gates. Thus, if a NOT gate's delay is  $d_{NOT}$ , an OR gate has delay of  $d_{OR}$ , and an AND gate has delay  $d_{AND}$ , then the total delay for both outputs of a full-adder is  $d_{FA} = d_{NOT} + d_{AND} + d_{OR}$ . Thus, at time  $t_0 + d_{FA}$ , we can trust that  $z_0$  and  $c_1$  are correct and will not change so long as the inputs x and y are unchanged.

Now for the catch:  $z_1$  and  $c_2$  cannot be trusted until the second full-adder has had sufficient

time to process its inputs. However, although  $x_1$  and  $y_1$  may have been presented to their full-adder at time  $t_0$ ,  $c_i$  will not be guanateed to be a correct input until  $t_0 + d_{FA}$ . Thus,  $z_1$  and  $c_2$  will not be reliable ouput values until  $t_0 + d_{FA} + d_{FA} = t_0 + 2d_{FA}$ .

This pattern continues:  $z_2$  and  $c_3$  are not reliable until time  $t_0 + 3d_{FA}$ ;  $z_3$  and  $c_4$  become reliable at time  $t_0 + 4d_{FA}$ . Thus, the delay for the complete 4-bit adder is  $4d_{FA}$ . This delay is dictated by the *critical path*—a path through the circuit from some input to some output where the sum of hte gate delays along that path is maximal for that circuit. Here, the critical path from, say,  $x_0$  to  $z_3$  flows through a sequence of gates whose cumulative delay is  $4d_{FA}$ . This critical path is not unique, as others (e.g., starting at  $y_0$  and ending at  $c_4$ ) have identical gate delay sums.

We have created a circuit that, given time  $4d_{FA}$  to do its work, will automatically add any two 4-bit whole numbers. This device is made of nothing but the simple gates that perform simple propositional logic operations, yet the device itself performs a task that is not itself a logic operation.

## 2.6 More propositional logic

We have now seen simple demonstrations of using logic operators (AND, OR, NOT) and devices that carry out those operations (*gates*) to automatically perform a task—integer addition—that is not itself propositional logic. Now that we have seen how logic can be used to perform computation, we must become somewhat more proficient in this type of logic.

### 2.6.1 Boolean algebra

When working with Boolean expressions, we can apply algebraic rules that are familiar to us. We can also apply a few rules that are valid for Boolean algebra, but not for traditional algebra. Specifically:

- Identity:

- OR: x + 0 = x

- AND: x1 = x

- Commutativity:

- OR: x + y = y + x

- AND: xy = yx

- Associativity:

- AND: x + (y + z) = (x + y) + z

- OR: x(yz) = (xy)z

- Distribution: x(y+z) = xy + xz

- **Zero:** x0 = 0

• One: x + 1 = 1

Finally, there are a pair of special rules known as *DeMorgan's Laws*:

$$\overline{xy} = \overline{x} + \overline{y}$$

$$\overline{x+y} = \overline{x}\overline{y}$$

With these rules, we can manipulate any Boolean expression. In particular, we can use these properties to establish the equivalence of expressions; we can also use the properties to simplify expressions. For example, consider the following transformation from one expression that performs the XOR operation to another:

$$x \oplus y$$

=  $(x + y)(\overline{xy})$

=  $(x + y)(\bar{x} + \bar{y})$

=  $\bar{x}x + x\bar{y} + \bar{x}y + \bar{y}y$

=  $0 + x\bar{y} + \bar{x}y + 0$

=  $x\bar{y} + \bar{x}y$

### 2.6.2 The generality of truth tables

No matter what combination of operators used to compose a logic function, a truth table can always be constructed that represents that function. For example, consider the following arbitrary, 3-input function:

$$z = \overline{(w \oplus \overline{xy})(\bar{w}\bar{x})}$$

This function has no intuitive or obvious "meaning." It is merely an arbitrarily constructed function. We can construct its truth table by carrying out the function on all possible inputs, as shown in Table 2.16.

This type of conversion from a logic function to a truth table is straightforward. However, it is less clear how to convert from an arbitrary truth table to a logic function. It is important to note that any different logic functions may produce the same truth table—that is, there are functions that are semantically equal but syntactically different. For example, consider these three simple functions:

$$z_A = (x+y)(\overline{xy})$$

$$z_B = (x+y)(\bar{x}\bar{y})$$

$$z_C = \bar{x}y + x\bar{y}$$

| w | x | y | $\overline{xy}$ | $\bar{w}\bar{x}$ | $w \oplus \overline{xy}$ | z |

|---|---|---|-----------------|------------------|--------------------------|---|

| 0 | 0 | 0 | 1               | 1                | 1                        | 0 |

| 0 | 0 | 1 | 1               | 1                | 1                        | 0 |

| 0 | 1 | 0 | 1               | 0                | 1                        | 1 |

| 0 | 1 | 1 | 0               | 0                | 0                        | 1 |

| 1 | 0 | 0 | 1               | 0                | 0                        | 1 |

| 1 | 0 | 1 | 1               | 0                | 0                        | 1 |

| 1 | 1 | 0 | 1               | 0                | 0                        | 1 |

| 1 | 1 | 1 | 0               | 0                | 1                        | 1 |

Table 2.16: Translating an arbitrarily chosen, 3-input logic function into a truth table by evaluating the components of the function and adding them to the truth table, building towards the final function.

Superficially, these are three different 2-input functions. However, they all implement the XOR operation, producing the same outputs for any given input.<sup>3</sup> Thus, for a given truth table, an arbitrary number of syntactically different functions will produce the correct semantic result. How can one systematically convert any truth table into a corresponding logic function?

#### 2.6.3 Normal forms

Consider our previous, arbitrarily chosen, 3-input logic function and the corresponding truth table shown in Table 2.16. We can use that truth table to produce a function of a specific syntactic form by following a set of mechanistic steps. To do so, we begin by listing the input values of w, x, and y that results in z = 1. Table 2.17 shows the six cases fitting that description. Along with each such input combination, the table also shows how each such set of input values can be translated into a *conjunctive term*—that is, expression of w, x, and y such that the three are combined by the AND operator. Moreover, for each such term, if the variable in question for that case should be a 1, then the variable is written in an unmodified, "positive" form; if the variable should be a 0, then it should be inverted by the NOT operator before being conjoined with the other variables. For example, in the case where z = 1 when w = 0, x = 1, and y = 0, then the conjunctive term we seek is  $\overline{wxy}$ .

Given these six conjunctive terms (in this example), we then *disjoin* them—that is, combine them with the OR operator. There sult is a complete expression of z:

$$z = \bar{w}x\bar{y} + \bar{w}xy + w\bar{x}\bar{y} + w\bar{x}y + wx\bar{y} + wxy$$

For any assignment of values to the input variables that should yield z = 1, exactly one of the conjoined terms will evaluate to 1. Since all of those conjoined terms are then disjoined to form the whole expression, having any one conjoined term evaluate to 1 is sufficient for the entire expression also to evaluate to 1. For example, consider the evaluation of w = 1,

$<sup>^{3}</sup>$ Try constructing a truth table that evaluates all three functions to convince yourself of their semantic equivalence.

| w | x | y | conjunctive term  |

|---|---|---|-------------------|

| 0 | 1 | 0 | $\bar{w}x\bar{y}$ |

| 0 | 1 | 1 | $ar{w}xy$         |

| 1 | 0 | 0 | $w ar{x} ar{y}$   |

| 1 | 0 | 1 | $w ar{x} y$       |

| 1 | 1 | 0 | $wxar{y}$         |

| 1 | 1 | 1 | wxy               |

Table 2.17: For an example 3-input function, the six combinations of input values that cause a result of z = 1 and the corresponding conjunctive terms.

| $\bar{w}x\bar{y}+$ | $= \bar{1}1\bar{0}+$ | = 011 + | = 0 + |

|--------------------|----------------------|---------|-------|

| $\bar{w}xy+$       | $\bar{1}10 +$        | 010 +   | 0 +   |

| $w\bar{x}\bar{y}+$ | $1\bar{1}\bar{0}+$   | 101 +   | 0 +   |

| $w\bar{x}y+$       | $1\bar{1}0+$         | 100 +   | 0 +   |

| $wx\bar{y}+$       | $11\bar{0}+$         | 111 +   | 1 +   |

| wxy                | 110                  | 110     | 0     |

|                    |                      |         | = 1   |

Table 2.18: Evaluating the example expression where w = 1, x = 1, and y = 0, where exactly one conjunctive term evaluates to 1, causing the whole disjoined set of terms to evaluate to 1 as well.

x = 1, and y = 0 shown in Table 2.18. Each row in this table shows one conjunctive term from the disjoined six, and then shows how each is evaluated to each a final result.

As you might expect, for any assignment of values to w, x, and y where the result is z = 0, **none** of the conjunctive terms will evaluate to 1. Thus, the disjoining of a collection of 0 results is always 0, yielding the correct answer for that case.

This form of expression—a collection of conjoined terms, with each such term combining each input or its inversion, with all such terms disjoined—is the *disjunctive normal form* (DNF), or the *or-of-ands* form. As we have just seen, **any** truth table can be converted into a DNF expression. A corrolary of this observation is that three logic operations—AND, OR, and NOT—are sufficient for composing any logic function. Thus, the gates that perform this three operations are also sufficient to implement a device that carries out any logic function.

Note that there is also a *conjunctive normal form* (CNF): a set of *disjunctive terms*, each of which contains all of the input variables (or their inversion), all conjoined to form an expression. For example, the following function is expressed in CNF:

$$z = (\bar{w} + x + \bar{y})(w + \bar{x} + \bar{y})(w + \bar{x} + y)$$

Because this form is not as intuitively derived from a truth table as DNF expressions, we will not use it. However, any DNF expression can, through algebraic manipulation, be transformed into a CNF expression and *vice versa*.

| x | $\overline{xx} = z$ |

|---|---------------------|

| 0 | 1                   |

| 1 | 0                   |

Table 2.19: The truth table for  $z = \overline{xx} = \overline{x}$ , showing NAND configured to perform the NOT operation.

Figure 2.7: A combinational circuit using only NAND gates to carry out the NOT operation.

#### 2.6.4 Minimal operators

The observation that AND/OR/NOT are sufficient to express any logic function poses the following question: *Do we need all three of those operators?* Can we compose any logic function from just two, or perhaps even one logic operator? Note that to prove that fewer operators are sufficient, we need only show how to compose the one or two operators such that they perform AND, OR, and NOT, whose sufficiency we have already demonstrated.

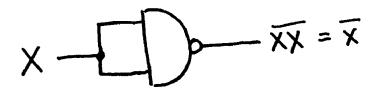

Let us consider the NAND operator, defined by the truth table shown in Table 2.12, and defined by the function  $z = \overline{xy}$ . Then let us see how this one operator can be composed with itself to carry out NOT, and, and OR.

**not** : Although NAND is a *binary operator* (that is, it operates on two 1-bit inputs), NOT is a *unary operator* (it operators on one 1-bit input). Thus, consider using the same variable for both of a NAND operator's inputs:

$$z = \bar{x} = \overline{xx}$$

That is, x is NAND'ed with itself. Since x is the only input, we can use the simplified truth table shown in Table 2.19 to prove that  $\overline{x} = \overline{xx}$ , and thus that NAND can be used to invert a value. Figure 2.7 shows the combinational circuit, using only a NAND-gate, that performs the NOT operation.

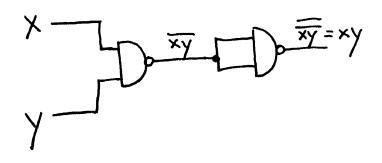

**and** : Now that we have established that NAND can perform the NOT operation, we can use both operators in determining how to perform AND using only NAND. The following expressions, as well as the truth table shown in Table 2.20, show the equivalence:

$$z = xy = \overline{\overline{xy}} = \overline{\overline{xyxy}}$$

| x | y | $\overline{xy}$ | $z = \overline{\overline{xy}} = xy$ |

|---|---|-----------------|-------------------------------------|

| 0 | 0 | 1               | 0                                   |

| 0 | 1 | 1               | 0                                   |

| 1 | 0 | 1               | 0                                   |

| 1 | 1 | 0               | 1                                   |

Table 2.20: The truth table for  $z = xy = \overline{\overline{xy}}$ , showing NAND configured to perform the AND operation.

Figure 2.8: A combinational circuit using only NAND gates to carry out the AND operation.

| x | y | $\bar{x}\bar{y}$ | $\overline{\bar{x}\bar{y}} = x + y$ |

|---|---|------------------|-------------------------------------|

| 0 | 0 | 1                | 0                                   |

| 0 | 1 | 0                | 1                                   |

| 1 | 0 | 0                | 1                                   |

| 1 | 1 | 0                | 1                                   |

Table 2.21: The truth table for  $z = x + y = \overline{x}\overline{y}$ , showing NAND configured to perform the OR operation.

Again, we can prove this equivalence with the truth table in Table 2.20; we can also see, in Figure 2.8 the combinational circuit that implements AND using only NAND gates.

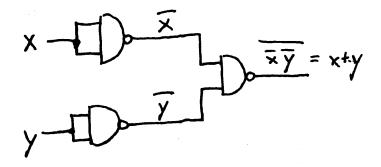

**or** : Finally, we have the ability, using only NAND gates, to perform NAND, AND, and NOT. With these three, we seek to perform the OR operation. The formula below shows the equivalence between an arrangement of NAND operations and the OR operation. Table 2.21 and Figure 2.9 show the truth table and combinational circuit, respectively, that reflect this formula.

$$z = x + y = \overline{x + y} = \overline{\bar{x}\bar{y}}$$

Figure 2.9: A combinational circuit using only NAND gates to carry out the OR operation.

**The big picture:** These three simple circuits, using only NAND gates, are sufficient building blocks to implement any logic function. Moreover, we will see that they are therefore sufficient to implement any computation. NOR is likewise sufficient; we leave it to the reader to develop AND, OR, and NOT expressions and circuits based solely on the NOR operator.

## 2.7 Circuit simplification

We can see from the 4-bit adder example that circuit structures for any non-trivial task are complex. For those constructing circuits by hand, each additional gate adds not only labor but also an opportunity for a miswiring error. For mass-produced circuits, each additional gate occupies valuable chip space, consumes more energy, and produces more waste heat.

Therefore, we have many reasons to simplify our circuits. Doing so requires simplifying the corresponding logic—that is, for a given truth table, finding the corresponding logic function that uses the fewest logic operators. Since each operator is implemented by a gate, these minimal functions yield the smallest circuits.

#### 2.7.1 Karnaugh maps for 2-input functions

Normal forms provide simple, mechanistic approaches top translating a truth table into a logic function. However, normal form functions are rarely minimal. Here, we examine an alternative method for t ranslating truth tables into logic functions—a method that, by finding certain patterns, allows us to create a minimal logic function.

Consider the NAND function, whose 2-input truth table is shown in Table 2.12. We can easily convert this truth table into a DNF logic function<sup>4</sup>:

$$z = \bar{x}\bar{y} + \bar{x}y + x\bar{y}$$

<sup>&</sup>lt;sup>4</sup>Although you can likely imagine a simpler function that this DNF form, note that your ability to do so stems from the inherent smallness and simplicity of any 2-input function. Suspend your intuitions about simpler functions for the purpose of this example; later examples will be more difficult, where you not immediately identify a simpler form.

Figure 2.10: The layout of a Karnaugh map for the 2-input NAND function.

Figure 2.11: A 2-input Karnaugh map, with rectangles encapsulating simplified conjunctive terms.

In order to devise a syntactically shorter function, we begin by writing our truth table in a special form, known as a Karnaugh map, as shown in Figure 2.10. For this map, the vertical axis is labeled with the possible values of x ( $\bar{x} \Leftrightarrow x = 0, x \Leftrightarrow x = 1$ ), while the horizontal axis is labeled analogously with the possible y values. Then, each position on the map corresponds to some specific choice of values for the two input variables. Moreover, that choice of values for the input variables corresponds to an output value for z. That z value should be placed in the aofrementioned location in the map, thus showing the function's result for those input values associated with that position.

Next, one must find **rectangles of 1's**. A rectangle that encoloses 1's with no 0's included identifies a simplified conjunctive term that will be part of a completed expression for the entire function, where the conjunctive term has factored out superfluous variables. Figure 2.11 shows the rectangles for a Karnaugh map of the NAND function. These rectangles can be horizontal or vertical, and they may overlap. Using this example, we can examine what each of these rectangles represent:

- $\alpha$ : This rectangle encapsulates two 1's, and thus two input patterns that cause the function to evaluate to 1, specifically x = 0, y = 0 and x = 0, y = 1. Notice that for both of these cases, x = 0. Graphically, we see that commonality in that  $\alpha$  spans  $\bar{y}$  and y columns, but stays within  $\bar{x}$  row.

- $\beta$ : Similarly, the two 1's encapsulated by this rectangle are produced by the pair of input patterns x = 0, y = 0 and x = 1, y = 0. This rectangle spands the rows  $\bar{x}$  and x, but stays within the column  $\bar{y}$ , thus graphically representing that y = 0.

Each rectangle represents a single conjunctive term that is simplified—that is, unlike a conjunctive term in DNF, it may not contain every input variable. Specifically, each rectangle represents a term composed of the common input variables (or their inversions), with those input variables that are not in common excluded. For example,  $\alpha$  represents the term  $\bar{x}$ . We can obtain this same simplification by applying Boolean algebraic rules to a DNF expression of the input patterns to which  $\alpha$  corresponds. That is:

$$\alpha = \bar{x}\bar{y} + \bar{x}y$$

If we factor out  $\bar{x}$ , apply the disjunctive ones property, and then the conjunctive identity property, we get:

$$\alpha = \bar{x}(\bar{y} + y) = \bar{x}1 = \bar{x}$$

Thus,  $\alpha$  here represents the term  $\bar{x}$ , which is a substantial simplification of  $\bar{x}\bar{y} + \bar{x}y$ . Similarly,  $\beta$  can be shown to represent  $\bar{y}$  as follows:

$$\beta = \bar{x}\bar{y} + x\bar{y} = \bar{y}(\bar{x} + x) = \bar{y}\mathbf{1} = \bar{y}$$

The terms represented by the rectangles can then be disjoined, thus forming the complete, simplified expression:

$z = \bar{x} + \bar{y}$

Notice that the two rectangles overlapped at  $\bar{x}\bar{y}$ . Such overlaps are valid. For the input pattern corresponding to an overlapping region, the consequence is that more than one of the conjunctive terms in the final expression will evaluate to 1. Here, when x = 0, y = 0, then  $\bar{x} = \bar{y} = 1$ . But since those terms are disjoined in z, whether one or both evaluates to 1 is irrelevant—the end result is that z = 1.

Thus, the rectangle & here prepresents the term X, which is a substantiality simplification of Xy + Xy. Similarly, the rectangle & spans the terms that concel, and is contained by the Erm that remains .  $\overline{xy} + x\overline{y} = \overline{y}(\overline{x} + x) = \overline{y}(1) = \overline{y}$ The terms represented by the rectandes can then disjoined, thus forming the complete, simplified expression:  $z = \overline{x} + \overline{y}$ Altotte @ Kamara map - 3 inputs The two-input example above shows most at the basics of using Karnaug meps to simplify logic functions, but 2-not functions are so simple that the value of the Karnaugh map is not obvice. In which is there is see inow to use this approach for a 3-impat function. Specifically, consider this approach for a 3-impat 0 6 S Þ No. of Lot of Lo  $\mathbb{O}$  $\delta$  $\langle \rangle$

48

Now consider the Karnaugh map for this same 3-input function: The the test of test o First, notice to let us write this function in DNF: Z = WXY + WXY + WXY + WXY + WXY Second, to before simplifying this lengthy expression, tet we share consider how the Karnawich map is configured. We have only too dimensions to the table, but we have three inputs to represent. So the main column labels specify not one, but two of the input variables — X and Y. The row tet Notice that there are four columns — one for each possible combination of XAT X and X with Y and Y. Meanwhile, w and w are the labels for the rows. The table therefore has ZXY=8 entries - one for each possible combinetion of input value for the w, x, and y. The is one additional, critical aspect of this table's configuration. Notice the progression of the column labels. Typically, the contain binary can the sequence follows the integers: OQ  $(\overline{xy})$ ; QI  $(\overline{xy})$ ; IX  $(x\overline{y})$ ; II (xy). However, the column labels follow a different progression: QQ  $(\overline{xy})$ ;  $\overline{E} QI (\overline{xy})$ ; II (xy);  $IO(x\overline{y})$ . Why the altered projession? Karnaugh maps reg For Karnaugh maps to

2

49

50

work—that is, for the rectangles to provide the correctly to identify factorizations of superfluous terms — then each test column label must have at one a term in comm with the labels on each adjacent term. That is, from one column to the next, the labels must have either an x, an x, a y, or a Fin common. If The standard counting sequence lacks this property. Specifically, if XY and XY are adjacent to one another, as the would be for the standard sequence, then those two columns have no term in common. In contrast, notice that the sequence on the example Karnargh map has this property; every column has a term in common with those a sjacant. Third, let us suse this Karnangh map to simplify the algebraic is the store pression ! > the the WHO I O Again, we tind rectages of I's. Note that each rectange must have a power-of-2 months size for for each dimension. That is, the rectangles may be 1x7, Zx1, ## 1x4,4x821, or Zx2. A 1x3 &, 3x1, Zx3, or 3x2 rectangle is invalid the because the 1's in such a rectangle would not have any all have terms in common. However, the valid rectangle sizes contain 15 all Atst which will have times in common. For example, ansider our three rectangles abore!

x) This rectangle spens wand w, so that term can be eliminated. The two I's contained by & both theo are contained in the column XX, and thus have those terms in common. This rectangle represents the in per simplified expression, the anigmetime term' XY. B) Like a, is and as can be dominated. Here, through, the X and y are the terms XY is the column that cartains this rectangle, so B represends: XY. 8) This 4×1 rectangle spans all combinations of x, x, y, and ¥. However, the rectangle is contained by the row w, and thus X represents. w. Notice that larger rectangles imply a larger = number of the factored terms, and thus shorter 25 Disjoin the three terms conjunctive terms, and our simplified torm  $Z = \overline{\chi y} + \chi y + \overline{W}$ . @ 4-input Karnavih maps

ON

t

'ny

Now that we see how to arrange two input variables along a single dimension of a Karneyh map, we can apply the same approach to both axes of the map, allowing for four input variables. I her us got again consider a orbitary truth table and that its corresponding Karningh map.

51

52

The truth take represents no 2 W Х 5 Q  $\mathcal{D}$ immediately or infurtuely re-Ś cognitzable function. It's DNF 0 Q  $\otimes$ is lengthy. 0 0 0 z = vwxy Ø N -STATEMAN STATEMAN 0 1 0 VWXY Q Ô. · vicence X VWX 2 -D VWX -----VW Q ..... 0 2 N VWXi VWXY Ø 2 VWXY Q - Section of Ø  $\mathcal{D}$ 8 VWXY+ 3 ----2 \$ VWXY + R 0 VWXY X The 4-input map is control in much like the 3-input, except The that both each dimension of マジ 8-VW the map is labeled with two 0 I input variables : no y and w  $\Delta$ The for the rows, and x and y for the columns. Again, each VW 5.1 Qrow or take column label must have at teast one term in connon with \$its advice adjacent labels. So, both rows and columns follow the special progression: QQ, QI, 11, 12.

She in Dist

In this example, we find five rectagles: two YXI rectagles (a, and B); one ZX2 rectangle (X); and two ZX1 rectangles (S and E). Again, each regtande encapsulates a set of Tis that represent input values that evaluate I for this function, and that can be expressed as to single conjuctive term. So: a) This rectangle spans every column and thus every combination of X they y, and their negations. However, it is also contained \$ within the row \$VW. Thus, if v=0 and w=0 then z=1 irrespective of the values of x and y. So, this rectangle represents the term:  $w=\overline{v}\overline{w}$ . B) Life This rectangle is analogous to x. Here, the map shows that, if x=0 and y=0, then z=1 no matter the values of  $x \neq u$  and w. Thus: XY. 8) This ZXZ rectangle is an interesting one in that it wraps around "from one edge of the map to the other. Third Third is, colomn XY is adjacent not only, to XY, but also to XY. Litensien These & spans I and y (vertically) as well as X and x (horizontelly by we wrapping around.) The rectangle is contained within the w salumas and the y columns -that is, it well and y=0, the values of V and X have no effect, since z=1 in all such cases. So! wy.

S) This 2×1 rectange is much like those of smaller maps. It is contained by the row vie and within the columns XY and XY. Thus, the 1's in this reatingle occur when Y = w = x = 1, irrespective of the value of Y. So: VWX.

E) This ZXI rectangle wraps around vertically, showing that  $V\overline{W}$  and  $\overline{V}\overline{W}$  are adjacent nows because of their common term  $\overline{W}$ . This rectangle is also contained within the column  $\overline{X}\overline{Y}$ . So, all 1's is this rectangle occur when  $\overline{X}$  W=0, X=Q, and  $\overline{Y}$ , regardless of the value of  $\underline{X}$  i  $\overline{W}\overline{X}\overline{Y}$ .

When we disjoin the terms implied by these five rectangles, we obtain the simplified expression:

> Z=VW+XY+WY+VWX+WXY x B 8 8 E

( Karnaugh maps are not casily extended beyond four inputs. For a tager higher arity finetrons, there are two optrons, neither of which we explore in depth:

D'Alsebiaie simplification: Like any algebra, the various properties of Boolean algebra allow expressions to be so manopulated and simplified. However, this method of simplification regimes protoce and construitly and this is before the scope of this book.

Circuit simplification algorithms i More advanced techniques, including those that perform extensive searches of the possible solutions, have been are performed by caref complex software. The most advanced of these tools are printing trade secrets. Because our geal is to inderstand how a simple system can be con-structed, and not how complex systems are optimized, this book will not address such tools.

De have down circuits for each circuit that we have created, we have assured that some input values—some collection of I's and Q's.- would be provided as the inputs to. From whence come these input values? So far, there are two Chorces! External value Direct inpot: By connecting an imput to a flow (e.g., a water pump for water-based gates; a OV for +5V electrical source for silicon gates). Thus, the value is a flow the source the source is the circuit and the provided by something external to the circuit and the logic it represents. € Output tinput chain: The output of some other gate may be used as the input to another — a fundamental characteristic that allows getes to us to implement composed logic functions using gates. Here the value is provided inter-nally, as one composed of a larger circuit. So far, all of our logic and circuits have been combinational, in that they are a functional, many to one mapping of <u>M</u> input values to <u>I</u> output value. That value is computed by a direct flow from the mpits, through the gates, and, after the delay diviated by the critical paths, to the artputs.

element.

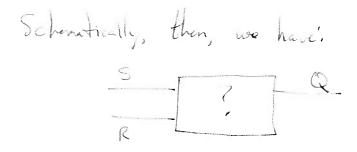

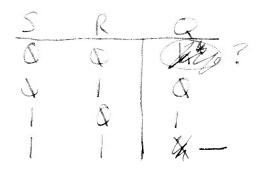

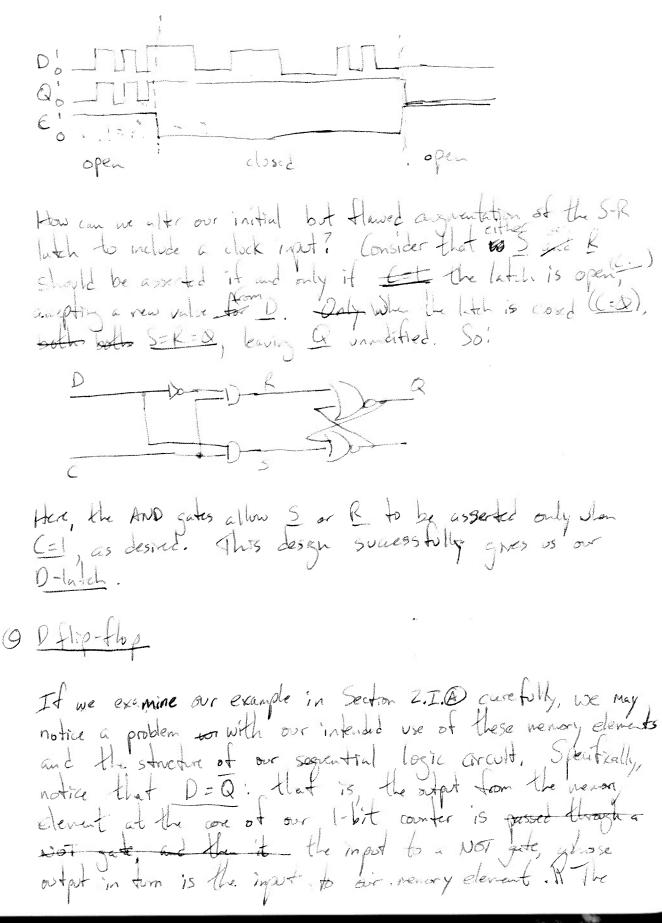

In order to see why the we would wint such menory elements, we will tonsider, in Section @. I. O, a simple the most simple of sequential logic arcists. This type what designings sever addressed more thoroughly in chapter (3), which is why we must address meniory elements thenisdues first. Note, however, that memory elevents will be just as tinchinated to competention as comprocessing itself i without data and stored in memory elevents, stepwise competing as in movint is impossible DE An motivation example: The toggle

Timeira that you want a device that will remember ore of two alternate between one of two possible states. For example, thereatwo small children are sherring a toy, and you want a device that remembers a which of the two children's torn it is. Or, for those familiar with the collegente baskethall you want to make the create the core of the respection arrow indicator. For bother devices, there is a single too botton that you would press to togle the state of the device' from Jethay's two to Ephrain's two group or vice verse; from the Amberst's possession at the part jung-ball to highlightens, or

vice versa.